并行测试中的工位间差异

从晶圆到系统级测试,实施并行测试可为用户带来诸多益处譬如降低成本,但是知之非艰,行之惟艰。

当测试工位数量增加,或在预烧炉或系统级测试模块中增加插槽数量时,就需要额外的工作去平衡热电所带来的挑战。

当然,测试单元资源的管理也需要投入一定的工程工作。

现在随着测试数据由系统管理和分析,这使得测试工程师团队和工厂车间既能管理单个芯片/单个测试单元的pass/fail标准,也能够处理多工位测试单元的测试数据。

多工位测试解决方案的目标

我们的目标是能够在所有细分领域非常方便的实施多工位方案,从而减少工程量,快速量产。

- 严格且有保证的设备规格参数,以消除通道间和测试设备间的差异对测试造成影响

- 多工位的测试程序软件编程模型快速且简单实现从x1至xN的转变

- 高效运行架构:降低多工位成本,减少测试工程量,实现优化的多工位解决方案

- 智能设备接口架构:能够将分散的测试机信号运送到大型应用区域的正确位置,传递对称工位(复制/粘贴)DIB器件布局信息,从而减小不同工位的走线差异

不同应用领域的多工位测试趋势

射频/毫米波

- 消费电子:8-16+工位

- 毫米波:2-4(探头有限)

对于射频/毫米波测试,测试灵敏度的持续提高和更高的测试频率会带来独特的挑战。其中部分原因是移动应用设备要不断降低功耗,这与待测芯片(DUT)更精确、更灵敏的Rx测试项紧密相关,连接中要求更高的带宽调制标准涉及更精确的误差向量幅度(EVM)测量,这些更灵敏的测量意味着在测试过程中对任何通道间差异或相互作用都有更高的易感性。

对于射频,一种解决方案是强化屏蔽通向DUT接口板的信号路径,并提供非常精确和校准控制的性能,其中芯片接口板尤为重要。射频信号传输允许电缆线靠近每个DUT工位连接,因此工作的重点是如何在电路板(PCB)到探头或引脚底座的最后约3英寸实现最佳设计。板卡需要支持去嵌(de-embed)功能,但这得对每个接口做正确的特性分析实验。

随着频率、测试精度及RF信号数量的增加,走线布设到内部阵列的连接且不带来信号衰减或干扰将会面临巨大挑战。先进的PCB设计理论,以及对制造差异的考虑,将决定你能否设计成功。对于更高频率的毫米波,还需要考虑一些其他因素,如邻近的金属结构(如引脚底座)。

数字

- MCU:~16至4K

- 先进的数字信号:1/2/4至16

数字芯片的种类繁多,从高工位数微控制器单元(MCU)和移动处理器到前沿的先进数字处理器(xPU、AI、网络设备)。

对于先进的数字器件,由于经济规模的扩大,移动应用处理器(MAP)的工位数量仍然是最大的。测试方案因市场而异,目前的工位数量从6到16个不等。

高性能运算芯片在测试(通常是扫描测试)期间会产生非常高的功率瞬变。这些大型芯片,有时从x1开始,但会推进到2-4个工位测试。如今,多工位面临的主要挑战是持续的高质量功率输送,以及不同工位间温度的控制。

对于移动和数据中心的应用来说,电源效率的Vmin 调整是非常关键的测试。不同工位上核心电源的任何偏差都可能导致数毫伏的差异,而这差异将会对芯片的能效以及测试良率造成影响。确保工位间的一致性是测试接口板(DIB)旁路电容和相关低阻抗驱动/回路布线的关键。在泰瑞达的UltraFLEXplus机台上,Broadside应用接口确保DIB电路的较大PCB区域位于设备连接和DUT之间(而非置于PCB侧面),这使得工位间的复制/粘贴排布真正成为可能,并且实现了布线一致性。这将节省测试工程师DIB板的设计时间,更重要的是,它避免因多工位问题而浪费的调试时间,甚至更糟的,因工位设计不满足需求而重新设计DIB的问题。

扫描数据量(以及由此导致的测试时间)的持续增长,推动人们转向高速串行扫描方法。这促使人们重新关注从整个信号路径到DUT的信号质量,速度达5至16 Gbps。不同工位之间的信号质量差异可能影响测试向量重测(测试时间增长),严重时会影响测试良率。就此而言,高质量信号测试设备以及工位一致的测试接口是关键。同样,自动测试设备(ATE)系统需要适应以及处理更高的数据带宽,并保持多工位产能效率,如下所述:

MCU则需要考虑:

- 智能卡设备将工位数量推到极限,最近在晶圆探针上成功达到4K工位。

- 因多工位而使用的大探头将会给整个卡盘上的温度带来巨大影响,如果不加以管理,这将影响芯片温度传感器的测量。

- 多工位之间的相关性必须依靠统计方式完成,与一个工位步进到单个芯片相比,其依赖的数据量更大。

- 安全交易芯片需要工位独一性的数据,而这些数据只能由设备工位独立提供。这会提高测试程序的复杂度——与服务器通信以获取密钥,对大量数据进行加密,并在测试时间内高效完成这些工作。

- 标准MCU的工位数通常比晶圆探针中要多(最多x64),对于封装测试则是从16个到128个不等(在最近的例子中高达x320条带测试)。这是个高度混合的市场,因此更高多工位的投资回报率(ROI)并不一定能证明增加接口成本的合理性,除非其批量变得很大。

- MCU的一个独特的多工位因素是响应时序变化,这通常与嵌入式闪存有关。一般来说,这是多工位经济性与工位特有的时序和数据管理工作之间的平衡。

汽车/功率

- 晶圆分类(WS):最多 x32

- 功能测试(FT):8-12用于较大引脚数的芯片,x32用于较少引脚数

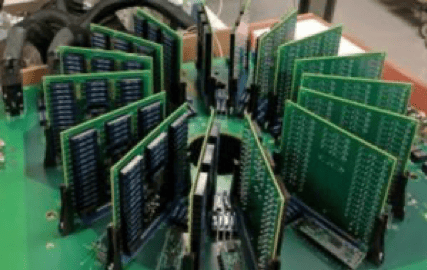

用于功率分立器件的16工位晶圆方案

多工位自动化测试方案能够满足巨大的DIB电路面积需求、功率的不断增加、更准确的测试以及终端市场安全因素的最高质量闸门等需求。

由于回流电流管理不当,复杂模拟IC的高电流测试极易受到多工位的影响。最大限度地解决DIB设计挑战的关键是拥有真正浮动的、专用的“低驱动”信号路径的设备。GaN和SiC技术的发展更容易出现电压和电流瞬变,这将加剧上述挑战。

Leakage、delta-leakage、Iddq、时序测试等关键测试项对布线差异更为敏感。施压前后的delta-leakage测试是一项关键的质量测试,所以就要求有高精度测量。任何布线错误都可能导致测试工位串行化(对每次测试都会产生数百毫秒的显著影响),或者需要重新设计或者生产PCB,从而增加成本和时间。

另一项关键测试是RDSon。最新的先进稳压器需要在40-100A负载下精确测量20mV电平。任何很小的工位间作用都会影响这一敏感测试。

车载上使用的现代电池管理系统(BMS)正将ATE系统的精度要求提高到在高通道数、高工位数应用上从未达到的水平。在高共模电压状态下,以可靠的高精度和低噪声向DUT提供激励从而为这些芯片的测试提供经济的解决方案。

泰瑞达ETS系统上浮动设备架构和拥有较大的应用区域的DIB接口,为多工位上一致性测试提供了最佳方案。

总结

总之,多工位测试的经济性仍是我们的追求。同最近几十年一样,同类型的多工位挑战仍然存在,其涉及的技术复杂度也在不断提高。大多数挑战是在芯片接口领域,从测试设备DIB连接到芯片连接都是如此。虽然不同的芯片领域各有其特有的接口挑战,但都要求测试工程师将其知识和专业技能进一步扩展到PCB布线领域。最优的测试系统可兼顾所有多工位因素,并使多工位测试解决方案变得快速且容易。

支持多工位测试驱动着许多设计因素,例如系统架构、设备硬件和软件,以及逐步增长的芯片接口领域。它是泰瑞达的核心使命,并已应用于我们从ATE到SLT系统的整个产品组合。

若要进一步了解泰瑞达用于先进计算机、汽车、无线和系统级测试应用的测试方案,请联系我们。

作者简介

Ed Seng是泰瑞达先进数字部门的战略营销经理。他在工程、应用和营销领域拥有20多年的经验,为前沿SoC、高速数字和串行接口开发提供测试解决方案,并为软件、设备和新ATE平台的发展指明方向。目前,Ed负责泰瑞达数字产品线在ATE领域的发展规划。他拥有宾夕法尼亚州立大学电子工程理学学士学位。